http://www.cyberciti.biz/faq/linux-cpuid-command-read-cpuid-instruction-on-linux-for-cpu

Is there a CPU-Z like a freeware/open source software that detects the central processing unit (CPU) of a modern personal computer in Linux operating system? How can I get detailed information about the CPU(s) gathered from the CPUID instruction, including the exact model of CPU(s) on Linux operating system?

There are three programs on Linux operating system that can provide CPUID information and these tools are useful to find out if specific advanced features such as virtualization, extended page tables, encryption and more:

Sample outputs:

Sample outputs:

Sample outputs:

Sample outputs:

Sample outputs:

Some important flags for sysadmins on Linux based system:

Here is complete information about one of cpu:

Sample outputs:

Is there a CPU-Z like a freeware/open source software that detects the central processing unit (CPU) of a modern personal computer in Linux operating system? How can I get detailed information about the CPU(s) gathered from the CPUID instruction, including the exact model of CPU(s) on Linux operating system?

There are three programs on Linux operating system that can provide CPUID information and these tools are useful to find out if specific advanced features such as virtualization, extended page tables, encryption and more:

- lscpu command – Show information on CPU architecture.

- x86info command – Show x86 CPU diagnostics.

- cpuid command – Dump CPUID information for each CPU. This is the closet tool to CPU-Z app on Linux.

x86info

x86info is a program which displays a range of information about the CPUs present in an x86 system.Install x86info on Debian / Ubuntu Linux

$ sudo apt-get install x86infoInstall x86info on Fedora Linux

$ sudo dnf install x86infoInstall x86info on RHEL/SL/CentOS Linux

$ sudo yum install x86infoExamples

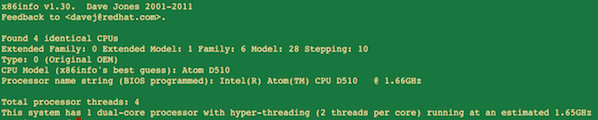

Simply type the following command:# x86infoSample outputs:

See TLB, cache sizes and cache associativity

# x86info -c Sample outputs:

x86info v1.30. Dave Jones 2001-2011 Feedback to |

See CPU feature flags like AES/FPU/SSE and more

# x86info -fSample outputs:

x86info v1.30. Dave Jones 2001-2011 Feedback to |

See MP table showing CPUs BIOS knows about

# x86info -mpSample outputs:

x86info v1.30. Dave Jones 2001-2011 Feedback to |

Show register values from all possible cpuid calls

# x86info -r.... .. eax in: 0x00000000, eax = 0000000a ebx = 756e6547 ecx = 6c65746e edx = 49656e69 eax in: 0x00000001, eax = 000106ca ebx = 00040800 ecx = 0040e31d edx = bfebfbff eax in: 0x00000002, eax = 4fba5901 ebx = 0e3080c0 ecx = 00000000 edx = 00000000 eax in: 0x00000003, eax = 00000000 ebx = 00000000 ecx = 00000000 edx = 00000000 eax in: 0x00000004, eax = 04004121 ebx = 0140003f ecx = 0000003f edx = 00000001 eax in: 0x00000005, eax = 00000040 ebx = 00000040 ecx = 00000003 edx = 00000010 eax in: 0x00000006, eax = 00000001 ebx = 00000002 ecx = 00000001 edx = 00000000 eax in: 0x00000007, eax = 00000000 ebx = 00000000 ecx = 00000000 edx = 00000000 eax in: 0x00000008, eax = 00000000 ebx = 00000000 ecx = 00000000 edx = 00000000 eax in: 0x00000009, eax = 00000000 ebx = 00000000 ecx = 00000000 edx = 00000000 eax in: 0x0000000a, eax = 07280203 ebx = 00000000 ecx = 00000000 edx = 00000503 eax in: 0x80000000, eax = 80000008 ebx = 00000000 ecx = 00000000 edx = 00000000 eax in: 0x80000001, eax = 00000000 ebx = 00000000 ecx = 00000001 edx = 20100800 eax in: 0x80000002, eax = 20202020 ebx = 20202020 ecx = 746e4920 edx = 52286c65 eax in: 0x80000003, eax = 74412029 ebx = 54286d6f ecx = 4320294d edx = 44205550 eax in: 0x80000004, eax = 20303135 ebx = 20402020 ecx = 36362e31 edx = 007a4847 eax in: 0x80000005, eax = 00000000 ebx = 00000000 ecx = 00000000 edx = 00000000 eax in: 0x80000006, eax = 00000000 ebx = 00000000 ecx = 02006040 edx = 00000000 eax in: 0x80000007, eax = 00000000 ebx = 00000000 ecx = 00000000 edx = 00000000 eax in: 0x80000008, eax = 00003024 ebx = 00000000 ecx = 00000000 edx = 00000000 .... ..To see all information, type:

# x86info -acpuid

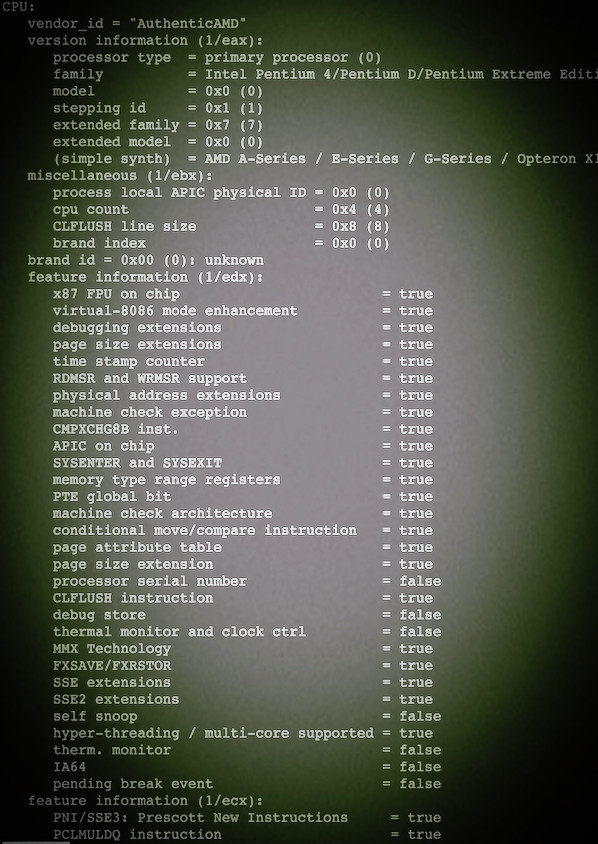

cpuid dumps detailed information about the CPU(s) gathered from the CPUID instruction, and also determines the exact model of CPU(s) from that information. It dumps all information available from the CPUID instruction. The exact collection of information available varies between manufacturers and processors. The following information is available consistently on all modern CPUs:- vendor_id

- version information (1/eax)

- miscellaneous (1/ebx)

- feature information (1/ecx)

Install cpuid on Debian / Ubuntu Linux

$ sudo apt-get install cpuidInstall cpuid on Fedora Linux

$ sudo dnf install cpuidInstall cpuid on RHEL/SL/CentOS Linux

$ sudo yum install cpuidExamples

Simply type the following command (this command provides lots of useful information including list of all features in human readable format):# cpuid

# cpuid | less

# cpuid | grep 'something'Sample outputs:

Display information only for the first CPU

# cpuinfo -1Use the CPUID instruction (default and very reliable)

# cpuinfo -iUse the CPUID kernel module (not seems to be reliable on all combinations of CPU type and kernel version)

# cpuinfo -kSearch for specific CPU feature

## Is virtualization supported (see below for flags)? ##

# cpuid -1 | egrep --color -iw 'vmx|svm|ept|vpid|npt|tpr_shadow|vnmi|flexpriority'

VMX: virtual machine extensions = true

## Is advanced encryption supported? ##

# cpuid -1 | egrep --color -i 'aes|aes-ni'

AES instruction = trueSome important flags for sysadmins on Linux based system:

- vmx – Intel VT-x, basic virtualization.

- svm – AMD SVM, basic virtualization.

- ept – Extended Page Tables, an Intel feature to make emulation of guest page tables faster.

- vpid – VPID, an Intel feature to make expensive TLB flushes unnecessary when context switching between guests.

- npt – AMD Nested Page Tables, similar to EPT.

- tpr_shadow and flexpriority – Intel feature that reduces calls into the hypervisor when accessing the Task Priority Register, which helps when running certain types of SMP guests.

- vnmi – Intel Virtual NMI feature which helps with certain sorts of interrupt events in guests.

Display information only for the first CPU

# cpuinfo -1Here is complete information about one of cpu:

CPU: vendor_id = "GenuineIntel" version information (1/eax): processor type = primary processor (0) family = Intel Pentium Pro/II/III/Celeron/Core/Core 2/Atom, AMD Athlon/Duron, Cyrix M2, VIA C3 (6) model = 0xd (13) stepping id = 0x7 (7) extended family = 0x0 (0) extended model = 0x2 (2) (simple synth) = Intel Core i7-3800/3900 (Sandy Bridge-E C2) / Xeon E5-1600/2600 (Sandy Bridge-E C2/M1), 32nm miscellaneous (1/ebx): process local APIC physical ID = 0x3 (3) cpu count = 0x20 (32) CLFLUSH line size = 0x8 (8) brand index = 0x0 (0) brand id = 0x00 (0): unknown feature information (1/edx): x87 FPU on chip = true virtual-8086 mode enhancement = true debugging extensions = true page size extensions = true time stamp counter = true RDMSR and WRMSR support = true physical address extensions = true machine check exception = true CMPXCHG8B inst. = true APIC on chip = true SYSENTER and SYSEXIT = true memory type range registers = true PTE global bit = true machine check architecture = true conditional move/compare instruction = true page attribute table = true page size extension = true processor serial number = false CLFLUSH instruction = true debug store = true thermal monitor and clock ctrl = true MMX Technology = true FXSAVE/FXRSTOR = true SSE extensions = true SSE2 extensions = true self snoop = true hyper-threading / multi-core supported = true therm. monitor = true IA64 = false pending break event = true feature information (1/ecx): PNI/SSE3: Prescott New Instructions = true PCLMULDQ instruction = true 64-bit debug store = true MONITOR/MWAIT = true CPL-qualified debug store = true VMX: virtual machine extensions = true SMX: safer mode extensions = true Enhanced Intel SpeedStep Technology = true thermal monitor 2 = true SSSE3 extensions = true context ID: adaptive or shared L1 data = false FMA instruction = false CMPXCHG16B instruction = true xTPR disable = true perfmon and debug = true process context identifiers = true direct cache access = true SSE4.1 extensions = true SSE4.2 extensions = true extended xAPIC support = true MOVBE instruction = false POPCNT instruction = true time stamp counter deadline = true AES instruction = true XSAVE/XSTOR states = true OS-enabled XSAVE/XSTOR = true AVX: advanced vector extensions = true F16C half-precision convert instruction = false RDRAND instruction = false hypervisor guest status = false cache and TLB information (2): 0x5a: data TLB: 2M/4M pages, 4-way, 32 entries 0x03: data TLB: 4K pages, 4-way, 64 entries 0x76: instruction TLB: 2M/4M pages, fully, 8 entries 0xff: cache data is in CPUID 4 0xb2: instruction TLB: 4K, 4-way, 64 entries 0xf0: 64 byte prefetching 0xca: L2 TLB: 4K, 4-way, 512 entries processor serial number: 0002-06D7-0000-0000-0000-0000 deterministic cache parameters (4): --- cache 0 --- cache type = data cache (1) cache level = 0x1 (1) self-initializing cache level = true fully associative cache = false extra threads sharing this cache = 0x1 (1) extra processor cores on this die = 0xf (15) system coherency line size = 0x3f (63) physical line partitions = 0x0 (0) ways of associativity = 0x7 (7) WBINVD/INVD behavior on lower caches = false inclusive to lower caches = false complex cache indexing = false number of sets - 1 (s) = 63 --- cache 1 --- cache type = instruction cache (2) cache level = 0x1 (1) self-initializing cache level = true fully associative cache = false extra threads sharing this cache = 0x1 (1) extra processor cores on this die = 0xf (15) system coherency line size = 0x3f (63) physical line partitions = 0x0 (0) ways of associativity = 0x7 (7) WBINVD/INVD behavior on lower caches = false inclusive to lower caches = false complex cache indexing = false number of sets - 1 (s) = 63 --- cache 2 --- cache type = unified cache (3) cache level = 0x2 (2) self-initializing cache level = true fully associative cache = false extra threads sharing this cache = 0x1 (1) extra processor cores on this die = 0xf (15) system coherency line size = 0x3f (63) physical line partitions = 0x0 (0) ways of associativity = 0x7 (7) WBINVD/INVD behavior on lower caches = false inclusive to lower caches = false complex cache indexing = false number of sets - 1 (s) = 511 --- cache 3 --- cache type = unified cache (3) cache level = 0x3 (3) self-initializing cache level = true fully associative cache = false extra threads sharing this cache = 0x1f (31) extra processor cores on this die = 0xf (15) system coherency line size = 0x3f (63) physical line partitions = 0x0 (0) ways of associativity = 0x13 (19) WBINVD/INVD behavior on lower caches = false inclusive to lower caches = true complex cache indexing = true number of sets - 1 (s) = 16383 MONITOR/MWAIT (5): smallest monitor-line size (bytes) = 0x40 (64) largest monitor-line size (bytes) = 0x40 (64) enum of Monitor-MWAIT exts supported = true supports intrs as break-event for MWAIT = true number of C0 sub C-states using MWAIT = 0x0 (0) number of C1 sub C-states using MWAIT = 0x2 (2) number of C2 sub C-states using MWAIT = 0x1 (1) number of C3 sub C-states using MWAIT = 0x1 (1) number of C4 sub C-states using MWAIT = 0x2 (2) number of C5 sub C-states using MWAIT = 0x0 (0) number of C6 sub C-states using MWAIT = 0x0 (0) number of C7 sub C-states using MWAIT = 0x0 (0) Thermal and Power Management Features (6): digital thermometer = true Intel Turbo Boost Technology = false ARAT always running APIC timer = true PLN power limit notification = true ECMD extended clock modulation duty = true PTM package thermal management = true digital thermometer thresholds = 0x2 (2) ACNT/MCNT supported performance measure = true ACNT2 available = false performance-energy bias capability = true extended feature flags (7): FSGSBASE instructions = false IA32_TSC_ADJUST MSR supported = false BMI instruction = false HLE hardware lock elision = false AVX2: advanced vector extensions 2 = false SMEP supervisor mode exec protection = false BMI2 instructions = false enhanced REP MOVSB/STOSB = false INVPCID instruction = false RTM: restricted transactional memory = false QM: quality of service monitoring = false deprecated FPU CS/DS = false intel memory protection extensions = false AVX512F: AVX-512 foundation instructions = false RDSEED instruction = false ADX instructions = false SMAP: supervisor mode access prevention = false Intel processor trace = false AVX512PF: prefetch instructions = false AVX512ER: exponent & reciprocal instrs = false AVX512CD: conflict detection instrs = false SHA instructions = false PREFETCHWT1 = false Direct Cache Access Parameters (9): PLATFORM_DCA_CAP MSR bits = 1 Architecture Performance Monitoring Features (0xa/eax): version ID = 0x3 (3) number of counters per logical processor = 0x4 (4) bit width of counter = 0x30 (48) length of EBX bit vector = 0x7 (7) Architecture Performance Monitoring Features (0xa/ebx): core cycle event not available = false instruction retired event not available = false reference cycles event not available = false last-level cache ref event not available = false last-level cache miss event not avail = false branch inst retired event not available = false branch mispred retired event not avail = false Architecture Performance Monitoring Features (0xa/edx): number of fixed counters = 0x3 (3) bit width of fixed counters = 0x30 (48) x2APIC features / processor topology (0xb): --- level 0 (thread) --- bits to shift APIC ID to get next = 0x1 (1) logical processors at this level = 0x2 (2) level number = 0x0 (0) level type = thread (1) extended APIC ID = 3 --- level 1 (core) --- bits to shift APIC ID to get next = 0x5 (5) logical processors at this level = 0x10 (16) level number = 0x1 (1) level type = core (2) extended APIC ID = 3 XSAVE features (0xd/0): XCR0 lower 32 bits valid bit field mask = 0x00000007 bytes required by fields in XCR0 = 0x00000340 (832) bytes required by XSAVE/XRSTOR area = 0x00000340 (832) XCR0 upper 32 bits valid bit field mask = 0x00000000 YMM features (0xd/2): YMM save state byte size = 0x00000100 (256) YMM save state byte offset = 0x00000240 (576) LWP features (0xd/0x3e): LWP save state byte size = 0x00000000 (0) LWP save state byte offset = 0x00000000 (0) extended feature flags (0x80000001/edx): SYSCALL and SYSRET instructions = true execution disable = true 1-GB large page support = true RDTSCP = true 64-bit extensions technology available = true Intel feature flags (0x80000001/ecx): LAHF/SAHF supported in 64-bit mode = true LZCNT advanced bit manipulation = false 3DNow! PREFETCH/PREFETCHW instructions = false brand = " Intel(R) Xeon(R) CPU E5-2650 0 @ 2.00GHz" L1 TLB/cache information: 2M/4M pages & L1 TLB (0x80000005/eax): instruction # entries = 0x0 (0) instruction associativity = 0x0 (0) data # entries = 0x0 (0) data associativity = 0x0 (0) L1 TLB/cache information: 4K pages & L1 TLB (0x80000005/ebx): instruction # entries = 0x0 (0) instruction associativity = 0x0 (0) data # entries = 0x0 (0) data associativity = 0x0 (0) L1 data cache information (0x80000005/ecx): line size (bytes) = 0x0 (0) lines per tag = 0x0 (0) associativity = 0x0 (0) size (Kb) = 0x0 (0) L1 instruction cache information (0x80000005/edx): line size (bytes) = 0x0 (0) lines per tag = 0x0 (0) associativity = 0x0 (0) size (Kb) = 0x0 (0) L2 TLB/cache information: 2M/4M pages & L2 TLB (0x80000006/eax): instruction # entries = 0x0 (0) instruction associativity = L2 off (0) data # entries = 0x0 (0) data associativity = L2 off (0) L2 TLB/cache information: 4K pages & L2 TLB (0x80000006/ebx): instruction # entries = 0x0 (0) instruction associativity = L2 off (0) data # entries = 0x0 (0) data associativity = L2 off (0) L2 unified cache information (0x80000006/ecx): line size (bytes) = 0x40 (64) lines per tag = 0x0 (0) associativity = 8-way (6) size (Kb) = 0x100 (256) L3 cache information (0x80000006/edx): line size (bytes) = 0x0 (0) lines per tag = 0x0 (0) associativity = L2 off (0) size (in 512Kb units) = 0x0 (0) Advanced Power Management Features (0x80000007/edx): temperature sensing diode = false frequency ID (FID) control = false voltage ID (VID) control = false thermal trip (TTP) = false thermal monitor (TM) = false software thermal control (STC) = false 100 MHz multiplier control = false hardware P-State control = false TscInvariant = true Physical Address and Linear Address Size (0x80000008/eax): maximum physical address bits = 0x2e (46) maximum linear (virtual) address bits = 0x30 (48) maximum guest physical address bits = 0x0 (0) Logical CPU cores (0x80000008/ecx): number of CPU cores - 1 = 0x0 (0) ApicIdCoreIdSize = 0x0 (0) (multi-processing synth): multi-core (c=8), hyper-threaded (t=2) (multi-processing method): Intel leaf 0xb (APIC widths synth): CORE_width=5 SMT_width=1 (APIC synth): PKG_ID=0 CORE_ID=1 SMT_ID=1 (synth) = Intel Xeon E5-1600/2600 (Sandy Bridge-E C2/M1), 32nm |

lscpu command example

You will get information about your CPU Architecture on Linux:$ lscpuSample outputs:

Architecture: x86_64 CPU op-mode(s): 32-bit, 64-bit Byte Order: Little Endian CPU(s): 32 On-line CPU(s) list: 0-31 Thread(s) per core: 2 Core(s) per socket: 8 Socket(s): 2 NUMA node(s): 2 Vendor ID: GenuineIntel CPU family: 6 Model: 45 Stepping: 7 CPU MHz: 2000.063 BogoMIPS: 4001.39 Virtualization: VT-x L1d cache: 32K L1i cache: 32K L2 cache: 256K L3 cache: 20480K NUMA node0 CPU(s): 0-7,16-23 NUMA node1 CPU(s): 8-15,24-31Of course you can also extract information from /proc/cpuinfo and /dev/cpu/* files:

$ less /proc/cpuinfo

No comments:

Post a Comment